# Intel® Desktop Board D865PERL Specification Update

Release Date: August 2004

Order Number: C41596-009

The Intel® Desktop Board D865PERL may contain design defects or errors known as errata, which may cause the product to deviate from published specifications. Current characterized errata are documented in this Specification Update.

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. INTEL PRODUCTS ARE NOT INTENDED FOR USE IN MEDICAL, LIFE SAVING, LIFE SUSTAINING APPLICATIONS.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined". Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Intel® desktop board D865PERL may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained from:

Intel Corporation P.O. Box 5937 Denver, CO 80217-9808

or call in North America 1-800-548-4725, Europe 44-0-1793-431-155, France 44-0-1793-421-777, Germany 44-0-1793-421-333, other Countries 708-296-9333

Intel, Pentium, Celeron, and the Intel logo are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

\* Other names and brands may be claimed as the property of others.

Copyright © 2003, 2004 Intel Corporation.

### **CONTENTS**

| REVISION HISTORY                                                       | V  |

|------------------------------------------------------------------------|----|

| PREFACE                                                                | vi |

| Specification Update for the Intel <sup>®</sup> Desktop Board D865PERL |    |

| GENERAL INFORMATION                                                    | 3  |

| SPECIFICATION CHANGES                                                  | 7  |

| ERRATA                                                                 | 12 |

| SPECIFICATION CLARIFICATIONS                                           | 15 |

| DOCUMENTATION CHANGES                                                  | 24 |

### **REVISION HISTORY**

| Date of Revision | Version | Description                                                                                                                                     |

|------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| June 2003        | -001    | This document is the first Specification Update for the Intel® Desktop Board D865PERL. Added Errata 1, 2 and Specification Clarifications 1, 2. |

| July 2003        | -002    | Added Specification Clarification 3.                                                                                                            |

| November 2003    | -003    | Added Specification Change 1, Specification Clarification 4 and Documentation Changes 1.                                                        |

| January 2004     | -004    | Added Specification Changes 2, 3. Added Errata 5-8. Added Specification Clarifications 5, 6.                                                    |

| March 2004       | -005    | Added Specification Change 4.                                                                                                                   |

| April 2004       | -006    | Added Erratum 9.                                                                                                                                |

| May 2004         | -007    | Added Specification Change 1. Updated Erratum 9. Added Specification Clarification 7.                                                           |

| July 2004        | -008    | Updated Specification Clarifications 3 and 7.                                                                                                   |

| August 2004      | -009    | Added Erratum 10.                                                                                                                               |

#### **PREFACE**

This document is an update to the specifications contained in the *Intel*<sup>®</sup> *Desktop Board D865PERL Technical Product Specification* (Order number C31764). It is intended for hardware system manufacturers and software developers of applications, operating systems, or tools. It will contain Specification Changes, Errata, Specification Clarifications, and Documentation Changes.

Refer to the *Intel*<sup>®</sup> *Pentium*<sup>®</sup> *4 Processor Specification Update* (Order number 249199) for specification updates concerning the Intel Pentium 4 processor and that may apply to the desktop board D865PERL. Unless otherwise noted in this document, it should be assumed that any processor errata for a given stepping are applicable to the Altered Assembly (AA) revision(s) associated with that stepping.

Refer to the Intel® 865PE Chipset: 82865PE Memory Controller Hub (MCH) Specification Update (Order Number 252523) for specification updates concerning the 82865PE MCH Controller and that may apply to the desktop board D865PERL. Unless otherwise noted in this document, it should be assumed that any MCH errata for a given stepping are applicable to the Altered Assembly (AA) revision(s) associated with that stepping.

Refer to the Intel® 82801EB I/O Controller Hub (ICH5R) / 82801ER I/O Controller Hub (ICH5) Specification Update (Order Number 252517) for specification updates concerning the 82801ER I/O Controller Hub and that may apply to the desktop board D865PERL. Unless otherwise noted in this document, it should be assumed that any ICH 5 errata for a given stepping are applicable to the Altered Assembly (AA) revision(s) associated with that stepping.

#### Nomenclature

**Specification Changes** are modifications to the current published specifications. These changes will be incorporated in the next release of the specifications.

**Errata** are design defects or errors. Characterized errata may cause the desktop board D865PERL's behavior to deviate from published specifications. Hardware and software designed to be used with any given Altered Assembly (AA) and BIOS revision level must assume that all errata documented for that AA and BIOS revision level are present on all desktop boards.

**Specification Clarifications** describe a specification in greater detail or further highlight a specification's impact to a complex design situation. These clarifications will be incorporated in the next release of the specifications.

**Documentation Changes** include typos, errors, or omissions from the current published specifications. These changes will be incorporated in the next release of the specifications.

# Specification Update for the Intel® Desktop Board D865PERL

### **GENERAL INFORMATION**

#### **Basic Desktop Board D865PERL Identification Information**

| AA Revision | BIOS Revision         | Notes |

|-------------|-----------------------|-------|

| C27648-206  | RL86510A.86A.0046.P03 | 1-5   |

| C27648-207  | RL86510A.86A.0052.P06 | 1-5   |

| C27648-208  | RL86510A.86A.0061.P09 | 1-5   |

| C27648-209  | RL86510A.86A.0071.P13 | 1-5   |

| C27648-210  | RL86510A.86A.0075.P15 | 1-5   |

| C26719-207  | RL86510A.86A.0046.P03 | 1-5   |

| C26719-208  | RL86510A.86A.0052.P06 | 1-5   |

| C26719-209  | RL86510A.86A.0056.P07 | 1-5   |

| C26719-210  | RL86510A.86A.0058.P08 | 1-5   |

| C26719-211  | RL86510A.86A.0061.P09 | 1-5   |

| C26719-212  | RL86510A.86A.0075.P13 | 1-5   |

| C26719-213  | RL86510A.86A.0075.P15 | 1-5   |

| C27646-206  | RL86510A.86A.0046.P03 | 1-5   |

| C27646-207  | RL86510A.86A.0052.P06 | 1-5   |

| C27646-208  | RL86510A.86A.0056.P07 | 1-5   |

| C27646-209  | RL86510A.86A.0058.P08 | 1-5   |

| C27646-210  | RL86510A.86A.0061.P09 | 1-5   |

| C27646-211  | RL86510A.86A.0075.P13 | 1-5   |

| C27646-212  | RL86510A.86A.0075.P15 | 1-5   |

| C27650-206  | RL86510A.86A.0046.P03 | 1-5   |

| C27650-207  | RL86510A.86A.0052.P06 | 1-5   |

| C27650-208  | RL86510A.86A.0056.P07 | 1-5   |

| C27650-209  | RL86510A.86A.0061.P09 | 1-5   |

| C27650-210  | RL86510A.86A.0071.P13 | 1-5   |

| C27650-211  | RL86510A.86A.0075.P15 | 1-5   |

| C40926-201  | RL86510A.86A.0052.P06 | 1-5   |

| C40926-202  | RL86510A.86A.0061.P09 | 1-5   |

| C40926-203  | RL86510A.86A.0071.P13 | 1-5   |

| C40926-204  | RL86510A.86A.0075.P15 | 1-5   |

### Intel® Desktop Board D865PERL Specification Update

#### NOTES:

- 1. The AA number is found on a small label on the component side of the board.

- 2. The 82865PE Chipset kit used on this AA revision consists of two components as follows:

| Device      | Stepping | S-Spec Numbers |

|-------------|----------|----------------|

| 82865PE MCH | A2       | SL722          |

| 82801EB ICH | A3       | SL73Z          |

| 82801ER ICH | А3       | SL742          |

- Refer to the Intel<sup>®</sup> Pentium<sup>®</sup> 4 Processor Specification Update (Order Number 249199) for errata related to the Pentium 4 processor and that may apply to the desktop board D865PERL.

- Refer to the Intel<sup>®</sup> 865PE Chipset: 82865PE Memory Controller Hub (MCH) Specification Update (Order Number 252524) for errata related to the 82865P MCH that may apply to the desktop board D865PERL.

- Refer to the Intel<sup>®</sup> 82801EB I/O Controller Hub (ICH5R) / 82801ER I/O Controller Hub (ICH5) Specification Update (Order Number 252517) for errata related to the 82801ER I/O Controller Hub that may apply to the desktop board D865PERL.

### Summary Table of Changes

The following table indicates the Specification Changes, Errata, Specification Clarifications, or Documentation Changes that apply to the Intel<sup>®</sup> desktop board D865PERL. Intel intends to fix some of the errata in a future revision of the desktop board, and to account for the other outstanding issues through documentation or specification changes as noted. This table uses the following notations:

### **CODES USED IN SUMMARY TABLE**

Doc: Document change or update that will be implemented.

PlanFix: This erratum may be fixed in a future revision of the desktop board, driver, or

BIOS.

Fixed: This erratum has been previously fixed.

NoFix: There are no plans to fix this erratum.

Shaded: This erratum is either new or modified from the previous version of the document.

|     | I        |                                                                                                                                              |  |

|-----|----------|----------------------------------------------------------------------------------------------------------------------------------------------|--|

| NO. | PLANS    | SPECIFICATION CHANGES                                                                                                                        |  |

| 1   | Doc      | Change to description of the SMBIOS specification listed in Table 3, Section 1.4                                                             |  |

| 2   | Doc      | Change to description of the SMBIOS specification listed in Table 3, Section 1.4                                                             |  |

| 3   | Doc      | Change to description of Section 2.11.1, DC Loading                                                                                          |  |

| 4   | Doc      | Change to Thermal Considerations, Section 2.12                                                                                               |  |

| 5   | Doc      | Change to description of Section 1.7.3.3, serial ATA RAID. Addition of RAID 1 support                                                        |  |

| NO. | PLANS    | ERRATA                                                                                                                                       |  |

| 1   | No Fix   | Audio driver creates a popping noise during operating system startup.                                                                        |  |

| 2   | Plan Fix | Front panel audio connector signals routed incorrectly.                                                                                      |  |

| 3   | Plan Fix | PCI slot 1 cannot be used with long PCI add-in cards                                                                                         |  |

| 4   | No Fix   | Advance jack sense may not recognize devices connected to a front panel audio port                                                           |  |

| 5   | No Fix   | Advance jack sense on boards with 6-channel audio will report "Microphone" for any device connected to the back panel microphone port (pink) |  |

| 6   | No Fix   | Advance jack sense will not detect devices connected to the Center/LFE and Surround ports                                                    |  |

| 7   | No Fix   | Advance jack sense may report amplified speakers as an array microphone when connected to the microphone port (pink)                         |  |

| 8   | No Fix   | An additional reboot may be required after installing audio drivers for Microsoft Windows* 98SE or Windows ME                                |  |

| 9   | Plan Fix | System memory may be reduced in excess of the amount of AGP aperture size when 4GB of system memory are used                                 |  |

| 10  | Plan Fix | Some systems may hang if the mouse is moved when entering standby mode                                                                       |  |

### Summary Table of Changes (cont)

| NO. | PLANS | SPECIFICATION CLARIFICATIONS                                                                         |

|-----|-------|------------------------------------------------------------------------------------------------------|

| 1   | Doc   | Add note that specifies Enhanced Mode IDE/Serial ATA requirements to Section 3.3.2, PCI IDE Support. |

| 2   | Doc   | Updates to the design specifications applicable to the desktop board D865PERL.                       |

| 3   | Doc   | Change to description of Table 28, Front Panel Audio Connector.                                      |

| 4   | Doc   | Clarification of SMBus routing                                                                       |

| 5   | Doc   | Clarification of DDR voltage                                                                         |

| 6   | Doc   | Clarification of Section 2.11.1, DC Loading                                                          |

| 7   | Doc   | Change to Description of Section 2.9.1, Front Panel Audio Connector/Jumper Block                     |

| NO. | PLANS | DOCUMENTATION CHANGES                                                                                |

| 1   | Doc   | Removal of Intel® branding from subtitle of Section 1.10.2                                           |

### **SPECIFICATION CHANGES**

The Specification Changes listed in this section apply to the *Intel*® *Desktop Board D865PERL Technical Product Specification* (Order Number C31764). All Specification Changes will be incorporated into a future version of that specification.

# 1. Change to Description of the SMBIOS Specification Listed in Table 3, Section 1.4

Table 3, Section 1.4, SMBIOS specification will change as follows:

Table 3. Specifications

| Reference<br>Name | Specification<br>Title       | Version, Revision Date, and Ownership                                                  | The information is available from                                  |

|-------------------|------------------------------|----------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| SMBIOS            | System<br>Management<br>BIOS | Version 2.3.2,<br>October 12, 2001,<br>Distributed Management<br>Taskforce, Inc (DMTF) | http://www.dmtf.org/stand<br>ards/documents/SMBIOS<br>/DSP0130.pdf |

# 2. Change to Description of the SMBIOS Specification Listed in Table 3, Section 1.4

Table 3, Section 1.4, SMBIOS specification will change as follows:

Table 3. Specifications

| Reference<br>Name | Specification<br>Title       | Version, Revision Date, and Ownership                                         | The information is available from                                  |

|-------------------|------------------------------|-------------------------------------------------------------------------------|--------------------------------------------------------------------|

| SMBIOS            | System<br>Management<br>BIOS | Version 2.3.4, December 6, 2002, Distributed Management Taskforce, Inc (DMTF) | http://www.dmtf.org/stand<br>ards/documents/SMBIOS/<br>DSP0134.pdf |

### 3. Change to Description of Section 2.11.1, DC Loading

Table 43, Section 2.11.1, DC Loading, will change in its entirety as follows:

### 2.11.1 DC LOADING

Table 43 lists the DC loading characteristics of the board.

Table 43. **DC Loading Characteristics**

|                 |          | DC Current at: |         |         |        |        |

|-----------------|----------|----------------|---------|---------|--------|--------|

| Mode            | DC Power | +3.3 V         | +5 V    | +12 V   | -12 V  | +5 VSB |

| Minimum loading | 190.00 W | 5.00 A         | 11.00 A | 9.00 A  | 0.03 A | 0.60 A |

| Maximum loading | 310.00 W | 11.00 A        | 15.00 A | 15.00 A | 0.10 A | 1.38 A |

#### 4. Change to Thermal Considerations, Section 2.12

Section 2.12, Thermal Considerations will change in its entirety as follows:

### 2.12 Thermal Considerations

### **A** CAUTION

The use of an Intel® Pentium® 4 processor operating above 2.80 GHz with this *Intel® desktop board requires the following:*

- A chassis with appropriate airflow to ensure proper cooling of the components on the board

- A processor fan heatsink that meets the thermal performance targets for Pentium 4 processors operating above 2.80 GHz

The use of an Intel Pentium 4 processor with 1 MB of L2 cache on this Intel desktop board requires the following:

- A chassis with a maximum internal ambient temperature of 38 Degrees Celsius

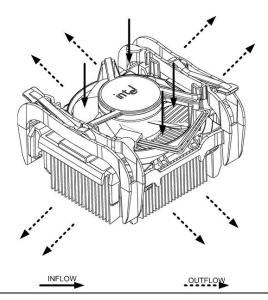

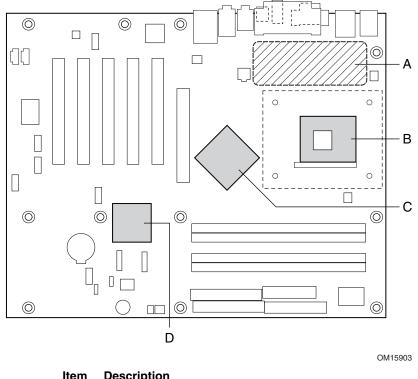

- A processor heatsink that provides omnidirectional airflow so that air is drawn across the processor voltage regulator area (item A in Figure 30). Figure 29a illustrates an omnidirectional airflow heatsink.

Figure 29a. Omnidirectional Airflow Heatsink

Failure to ensure appropriate airflow may result in reduced performance of both the processor and/or voltage regulator or, in some instances, damage to the desktop board. For a list of chassis that have been tested with Intel<sup>®</sup> desktop boards please refer to the following website:

#### http://developer.intel.com/design/motherbd/cooling.htm

All responsibility for determining the adequacy of any thermal or system design remains solely with the reader. Intel makes no warranties or representations that merely following the instructions presented in this document will result in a system with adequate thermal performance.

### **CAUTION**

Ensure that the ambient temperature does not exceed the Desktop Board D865PERL's maximum operating temperature. Failure to do so could cause components to exceed their maximum case temperature and malfunction. For information about the maximum operating temperature, see the environmental specifications in Section 2.14.

### **A** CAUTION

Ensure that proper airflow is maintained in the processor voltage regulator circuit. Failure to do so may result in damage to the voltage regulator circuit. The processor voltage regulator area (item A in Figure 30) can reach a temperature of up to 85 °C in an open chassis.

Figure 30 shows the locations of the localized high temperature zones.

| Item | Description                           |

|------|---------------------------------------|

| Α    | Processor voltage regulator area      |

| В    | Processor                             |

| С    | Intel® 82865PE MCH                    |

| D    | Intel® 82801EB ICH5 or 82801ER ICH5-R |

Figure 30. Localized High Temperature Zones

Table 45 provides maximum case temperatures for components on the Desktop Board D865PERL that are sensitive to thermal changes. The operating temperature, current load, or operating frequency could affect case temperatures. Maximum case temperatures are important when considering proper airflow to cool the Desktop Board D865PERL.

**Table 45.** Thermal Considerations for Components

| Component                                | Maximum Case Temperature                                                                     |

|------------------------------------------|----------------------------------------------------------------------------------------------|

| Intel® Pentium® 4 processor              | For processor case temperature, see processor datasheets and processor specification updates |

| Intel® 82865PE MCH                       | 99 °C (under bias)                                                                           |

| Intel® 82801EB ICH5 or<br>82801ER ICH5-R | 115 °C (under bias)                                                                          |

| For information about                                          | Refer to             |

|----------------------------------------------------------------|----------------------|

| Intel Pentium 4 processor datasheets and specification updates | Section 1.2, page 16 |

# 5. Change to Description of Section 1.7.3.3, Serial ATA RAID. Addition of RAID 1 Support

Section 1.7.3.3 will change in its entirety as follows:

### 1.7.3.3 Serial ATA RAID

The ICH5-R supports RAID (Redundant Array of Independent Drives) level 0 and level 1 on the Serial ATA ports. RAID 0 provides the ability to support striping. Two physical drives, of identical size, can be teamed together to create one logical drive. As data is written or retrieved from the logical drive, both drives operate in parallel, thus increasing the throughput. RAID 1 provides the support of disk mirroring. Data is written simultaneously to two physical drives, of identical size, providing fault tolerance if one of the two drives fails.

#### ■ NOTE

The ICH5-R provides support for RAID O, RAID 1 and RAID boot in Windows\* XP and Windows 2000 only.

#### **ERRATA**

# 1. Audio Driver Creates a Popping Noise During Operating System Startup

**PROBLEM:** The audio jack-sensing feature requires reading the impedance of the device connected to the audio jack. A voltage is needed so a current can be measured, and the impedance is derived from the voltage and current. The application of the voltage results in a popping noise that is emitted from the speakers.

**IMPLICATION:** A popping noise from the speakers may be heard at the end of the operating system startup tune, while loading Microsoft Windows operating systems.

WORKAROUND: None.

STATUS: This erratum will not be fixed.

### 2. Front Panel Audio Connector Signals Routed Incorrectly

**PROBLEM:** The front panel audio connector pin definition is not correct. Pin 4 is defined as +5 V and should be ground. Pin 7 is defined as ground and should be +5V.

**IMPLICATION:** Front panel audio cards that route their +5 V rail to Pin 4 will not function correctly. **WORKAROUND:** Front panel audio cards that require +5 V should route the +5 V rail to Pin 7.

**STATUS:** This erratum may be fixed in a future hardware revision.

### 3. PCI Slot 1 Cannot be Used With Long PCI Add-in Cards

PROBLEM: A tall capacitor is located 3 ¼ inches behind PCI slot 1.

IMPLICATION: PCI cards conforming to the PCI specification but exceed 8 inches in length, may not be

useable in PCI slot 1.

WORKAROUND: None.

**STATUS:** This erratum may be fixed in a future hardware revision.

### 4. Advance Jack Sense May Not Recognize Devices Connected to a Front Panel Audio Port

**PROBLEM:** The advanced jack sense with Auto Topology Switching, that is used by the audio codec to recognize what device is connected to an audio port, may fail to report devices connected to a front-panel port.

**IMPLICATION:** Devices connected through a front panel audio port will be detected and function correctly, but the advance jack sense wizard will only report the device at start up.

WORKAROUND: None.

STATUS: This erratum will not be fixed.

### 5. Advance Jack Sense on Boards with 6-Channel Audio Will Report "Microphone" for Any Device Connected to the Back Panel Microphone Port (Pink)

**PROBLEM:** For boards with 6-channel audio, the advanced jack sense with Auto Topology Switching, that is used by the audio codec to recognize what device is connected to an audio port, will report "Microphone" for any device connected to the back panel pink microphone port.

**IMPLICATION:** The advanced jack sense wizard will report any device connected through the back panel microphone port to be a "Microphone" and the wizard will prompt the user to verify this detection assumption.

WORKAROUND: None.

STATUS: This erratum will not be fixed.

### 6. Advance Jack Sense Will Not Detect Devices Connected to the Center/LFE and Surround Ports

**PROBLEM:** Polling devices connected to the Center/LFE and Surround port would cause popping noise once speakers are connected. Due to this anomaly, the advance jack sense wizard will not poll and report devices connected to the Center/LFE and Surround ports although these devices will work correctly.

**IMPLICATION:** Devices connected to the Center/LFE or Surround port will be detected and function correctly, but the advance jack sense wizard will not poll and report the device.

WORKAROUND: None.

STATUS: This erratum will not be fixed.

# 7. Advance Jack Sense May Report Amplified Speakers as an Array Microphone When Connected to The Microphone Port (Pink)

**PROBLEM:** The presence of voltage bias on the microphone jack during the detection phase is required for accurate detection, but amplified speakers and array microphones have very similar impedance values.

**IMPLICATION:** Amplified speakers will be detected and function correctly, but the advance jack sense wizard may report the device as an array microphone.

WORKAROUND: None.

**STATUS:** This erratum will not be fixed.

### 8. An Additional Reboot May Be Required After Installing Audio Drivers for Microsoft Windows 98SE or Windows ME

**PROBLEM:** An application post-installer completes the driver installation and requires an additional reboot to get full functionality in Windows 98SE or Windows ME.

IMPLICATION: An additional reboot is required after installing audio drivers for Windows 98SE or

Windows ME.

WORKAROUND: None.

STATUS: This erratum will not be fixed.

# 9. System Memory May Be Reduced in Excess of the Amount of AGP Aperture Size When 4GB of System Memory are Used

**PROBLEM:** The AGP aperture size setting in the system BIOS will consume, from available system memory, 2 times the amount applied in the AGP aperture setting when the maximum of 4 GB of system memory is installed.

**IMPLICATION:** When 4GB of system memory are used, and system memory is allocated to AGP aperture size in BIOS Setup, available system memory may be reduced by twice the amount allocated. A similar impact to available system memory may occur from any allocation of system memory when 4 GB of system memory is used. For example, increasing the video frame buffer in BIOS may also reduce available memory in excess of the amount requested.

WORKAROUND: None.

**STATUS:** This erratum may be fixed in a future BIOS revision.

# 10. Some Systems May Hang if the Mouse is Moved When Entering Standby Mode

**PROBLEM:** Moving the mouse after placing the system into standby with the mouse may cause the system to immediately awaken and hang.

**IMPLICATION:** The system may hang if the user is moving the mouse directly after using the mouse to place the system into standby mode.

WORKAROUND: None.

**STATUS:** This erratum may be fixed in a future board revision.

### SPECIFICATION CLARIFICATIONS

The Specification Clarifications listed in this section apply to the *Intel*® *Desktop Board D865PERL Technical Product Specification* (Order Number C31764). All Specification Clarifications will be incorporated into a future version of that specification.

# 1. Add Note That Specifies Enhanced Mode IDE/Serial ATA Requirements to Section 3.3.2, PCI IDE Support

In section 3.3.2, PCI IDE Support, the following note will be added.

### ■ NOTE

The Enhanced mode IDE/Serial ATA BIOS option requires support for resources up to a maximum six devices, and has been tested with Windows 2000 and Windows XP. This BIOS option should be set to Legacy mode when used with operating systems that support a maximum of two IDE channels (four devices).

# 2. Updates to the Design Specifications Applicable to the Desktop Board D865PERL

Table 3, section 1.4, Design Specification will be replaced in its entirety as follows.

### 1.4 Design Specifications

Table 3 lists the specifications applicable to the Desktop Board D865PERL.

Table 3. Specifications

| Reference<br>Name       | Specification<br>Title                                                                         | Version, Revision Date, and Ownership                                                               | The information is available from                                      |

|-------------------------|------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|

| IEEE Standard for a Ins |                                                                                                | November 8, 2001,<br>Institute of Electrical and<br>Electronic Engineers.                           | http://standards.ieee.org/catal<br>og/olis/busarch.html                |

|                         | IEEE Std 1394a-2000,<br>IEEE Standard for a<br>High Performance<br>Serial Bus –<br>Amendment 1 | June 29, 2000,<br>Institute of Electrical and<br>Electronic Engineers.                              | http://standards.ieee.org/catal<br>og/olis/busarch.html                |

| AC '97                  | Audio Codec '97                                                                                | Revision 2.2,<br>September 2000,<br>Intel Corporation.                                              | ftp://download.intel.com/labs/<br>media/audio/download/ac97r<br>22.pdf |

| ACPI                    | Advanced Configuration and Power Interface Specification                                       | Version 1.0b, February 08, 1999, Intel Corporation, Microsoft Corporation, and Toshiba Corporation. | http://www.acpi.info/spec10b.<br>htm                                   |

| AGP                     | Accelerated Graphics Port Interface Specification                                              | Revision 3.0,<br>September 1, 2002<br>Intel Corporation.                                            | http://www.agpforum.org/spe<br>cs_specs.htm                            |

| ASF                     | Alert Standard Format<br>(ASF) Specification                                                   | Version 1.03,<br>June 20, 2001,<br>DMTF,<br>Intel Corporation.                                      | http://www.dmtf.org/standard<br>s/documents/ASF/DSP0114.<br>pdf        |

Table 3.

Specifications (continued)

| Reference<br>Name | Specification Version, Revision Date and Ownership                                   |                                                                                | The information is available from                                                                       |

|-------------------|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| ATA/<br>ATAPI-5   | Information Technology-AT Attachment with Packet Interface - 5 (ATA/ATAPI-5)         | Revision 3, February 29, 2000, Contact: T13 Chair, Seagate Technology.         |                                                                                                         |

| ATX               | ATX Specification                                                                    | Version 2.1,<br>June 2002,<br>Intel Corporation.                               | http://www.formfactors.org/developer/specs/atx/atx2 1.pdf                                               |

| ATX12V            | ATX/ATX12V Power<br>Supply Design Guide                                              | Version 1.2,<br>August 2000,<br>Intel Corporation.                             | http://www.formfactors.org/developer/specs/atx/atxspecs.htm                                             |

| BIS               | Boot Integrity Services<br>(BIS) Application<br>Programming Interface<br>(API)       | Version 1.0,<br>August 4, 1999,<br>Intel Corporation.                          | http://www.intel.com/labs/ma<br>nage/wfm/wfmspecs.htm                                                   |

| DDR<br>SDRAM      | Double Data Rate<br>(DDR) SDRAM<br>Specification                                     | Version 2.0, May 2002, JEDEC Solid State Technology Association.               | http://www.jedec.org/                                                                                   |

|                   | Design Specification for<br>a 184 Pin DDR<br>Unbuffered DIMM                         | Revision 1.0,<br>October 2001,<br>JEDEC Solid State<br>Technology Association. | http://www.jedec.org/                                                                                   |

|                   | Intel <sup>®</sup> JEDEC DDR<br>200/266 Unbuffered<br>DIMM Specification<br>Addendum | Revision 0.9,<br>September 27, 2001,<br>Intel Corporation.                     | http://developer.intel.com/tec<br>hnology/memory/index.htm                                              |

| EHCI              | Enhanced Host<br>Controller Interface<br>Specification for<br>Universal Serial Bus   | Revision 1.0,<br>March 12, 2002,<br>Intel Corporation.                         | http://developer.intel.com/tec<br>hnology/usb/download/ehci-<br>r10.pdf                                 |

| EPP               | IEEE Std 1284.1-1997<br>(Enhanced Parallel<br>Port)                                  | Version 1.7, 1997,<br>Institute of Electrical and<br>Electronic Engineers.     | http://standards.ieee.org/read<br>ing/ieee/std_public/descriptio<br>n/busarch/1284.1-<br>1997_desc.html |

Table 3. Specifications (continued)

| Reference<br>Name | Specification<br>Title                                               | Version, Revision Date and Ownership                                                                                                                            | The information is available from                                      |

|-------------------|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|

| El Torito         | Bootable CD-ROM<br>Format Specification                              | Version 1.0,<br>January 25, 1995,<br>Phoenix Technologies<br>Limited and International<br>Business Machines<br>Corporation.                                     | http://www.phoenix.com/reso<br>urces/specs-cdrom.pdf                   |

| LPC               | Low Pin Count Interface<br>Specification                             | Revision 1.0,<br>September 29, 1997,<br>Intel Corporation.                                                                                                      | http://www.intel.com/design/c<br>hipsets/industry/lpc.htm              |

| OHCI              | OpenHCI – Open Host<br>Controller Interface<br>Specification for USB | Release 1.0a, October 10, 1996, Compaq Computer Corp., Microsoft Corporation, and National Semiconductor Corp.                                                  | http://h18000.www1.hp.com/p<br>roductinfo/development/open<br>hci.html |

| PCI               | PCI Local Bus<br>Specification                                       | Revision 2.2,<br>December 18, 1998,<br>PCI Special Interest<br>Group.                                                                                           | http://www.pcisig.com/specifications                                   |

|                   | PCI Bus Power<br>Management Interface<br>Specification               | Revision 1.1,<br>December 18, 1998,<br>PCI Special Interest<br>Group.                                                                                           | http://www.pcisig.com/specifications                                   |

| Plug and<br>Play  | Plug and Play BIOS<br>Specification                                  | Version 1.0a, May 5, 1994, Compaq Computer Corporation, Phoenix Technologies Limited, and Intel Corporation.  http://www.microsoft.cor dc/hwdev/tech/PnP/defa p |                                                                        |

| PXE               | Preboot Execution<br>Environment                                     | Version 2.1,<br>September 20, 1999,<br>Intel Corporation.                                                                                                       | ftp://download.intel.com/labs/<br>manage/wfm/download/pxesp<br>ec.pdf  |

Table 3.

Specifications (continued)

| Reference<br>Name    | Specification<br>Title                                 | Version, Revision Date and Ownership                                                                                                                                                                                                                                                                                    | The information is available from                      |

|----------------------|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|

| Serial ATA<br>(SATA) | Serial ATA: High<br>Speed Serialized AT<br>Attachment  | Revision 1.0, August 29, 2001, APT Technologies, Inc., Dell Computer Corporation, IBM Corporation, Intel Corporation, Maxtor Corporation, and Seagate Technology.                                                                                                                                                       | http://www.serialata.com/                              |

| SMBIOS               | System Management<br>BIOS                              | Version 2.3.1, March 16, 1999, American Megatrends Incorporated, Award Software International Incorporated, Compaq Computer Corporation, Dell Computer Corporation, Hewlett- Packard Company, Intel Corporation, International Business Machines Corporation, Phoenix Technologies Limited, and SystemSoft Corporation. | http://www.dmtf.org/download<br>/standards/DSP0119.pdf |

| UHCI                 | Universal Host<br>Controller Interface<br>Design Guide | Revision 1.1,<br>March 1996,<br>Intel Corporation.                                                                                                                                                                                                                                                                      | http://developer.intel.com/des<br>ign/USB/UHCI11D.htm  |

Table 3.

Specifications (continued)

| Reference<br>Name | Specification<br>Title                | Version, Revision Date and Ownership                                                                                                                                                                              | The information is available from                     |

|-------------------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| USB               | Universal Serial Bus<br>Specification | Revision 2.0, April 27, 2000, Compaq Computer Corporation, Hewlett-Packard Company, Lucent Technologies Inc., Intel Corporation, Microsoft Corporation, NEC Corporation, and Koninklijke Philips Electronics N.V. | http://www.usb.org/developer<br>s/docs.html           |

| WfM               | Wired for Management<br>Baseline      | Version 2.0,<br>December 18, 1998,<br>Intel Corporation.                                                                                                                                                          | http://www.intel.com/labs/ma<br>nage/wfm/wfmspecs.htm |

### 3. Change to Description of Table 28, Front Panel Audio Connector

Table 28, Front Panel Audio Connector will change in its entirety as follows:

**Table 28.** Front Panel Audio Connector

| Pin | Signal Name                  | Pin | Signal Name          |

|-----|------------------------------|-----|----------------------|

| 1   | Mono Mic in (Stereo Mic 1)   | 2   | Ground               |

| 3   | Mono Mic Bias (Stereo Mic 2) | 4   | +5 V                 |

| 5   | RIGHT_OUT                    | 6   | Right channel return |

| 7   | No connect                   | 8   | Key                  |

| 9   | LEFT_OUT                     | 10  | Left channel return  |

### 4. Clarification of SMBus Routing

Section 2.8.2.1 will change in its entirety as follows:

### 2.8.2.1 Expansion Slots

The Desktop Board D865PERL has the following expansion slots:

- AGP connector: The AGP connector is keyed for Universal 0.8 V AGP 3.0 cards or 1.5 V AGP 2.0 cards only. Do not install a legacy 3.3 V AGP card. The AGP connector is not mechanically compatible with legacy 3.3 V AGP cards

- Five PCI rev 2.2 compliant local bus slots: The SMBus is routed to PCI bus connector 2 only (ATX expansion slot 6). PCI add-in cards with SMBus support can access sensor data and other information residing on the Desktop Board D865PERL.

### **⇒** NOTE

The SMBus routing to the PCI bus connectors does not conform to the PCI Engineering Change Notice (ECN) "Addition of the SMBus to the PCI Connector ECN", dated October 5th, 2000. The ECN specifies that SMBus signals must be routed to all PCI bus connectors. On this board, SMBus signals are routed to PCI bus connector 2 only.

Add-in cards that implement PCI bus connector pins A40 and A41 for any purpose other than SMBCLK (SMBus clock) and SMBDAT (SMBus data) should not be installed in PCI bus connector 2.

| For information about                          | Refer to                                                             |

|------------------------------------------------|----------------------------------------------------------------------|

| Addition of the SMBus to the PCI Connector ECN | http://www.pcisig.com/data/s<br>pecifications/smb_ecn_0405<br>01.pdf |

#### **⇒** NOTE

This document references back-panel slot numbering with respect to processor location on the board. The AGP slot is not numbered. PCI slots are identified as PCI slot #x, starting with the slot closest to the processor. Figure 22 on page 68 illustrates the board's PCI slot numbering.

### 5. Clarification of DDR Voltage

Section 1.6.1, Memory Features, will change as follows:

#### 1.6.1 MEMORY FEATURES

The Desktop Board D865PERL has four DIMM sockets and supports the following memory features:

- 2.6 V (only) 184-pin DDR SDRAM DIMMs with gold-plated contacts

- Unbuffered, single-sided or double-sided DIMMs with the following restriction:

- Double-sided DIMMS with x16 organization are not supported.

- 4 GB maximum total system memory. Refer to Section 2.2.1 on page 51 for information on the total amount of addressable memory.

- Minimum total system memory: 64 MB

- Non-ECC DIMMs

- Serial Presence Detect

- DDR400, DDR333, and DDR266 SDRAM DIMMs

### 6. Clarification of Section 2.11.1, DC Loading

Clarification to Section 2.11.1, DC Loading, will be added as follows:

### 2.11.1 DC LOADING

Table 43 lists the DC loading characteristics of the board. This data is based on a DC analysis of all active components within the board that impact its power delivery subsystems. The analysis does not include PCI add-in cards. Minimum values assume a light load placed on the board that is similar to an environment with no applications running and no USB current draw. Maximum values assume a load placed on the board that is similar to a heavy gaming environment with a 500 mA current draw per USB port. These calculations are not based on specific processor values or memory configurations but are based on the minimum and maximum current draw possible from the board's power delivery subsystems to the processor, memory, and USB ports.

Use the datasheets for add-in cards, such as PCI and AGP, to determine the overall system power requirements. The selection of a power supply at the system level is dependent on the system's usage model and not necessarily tied to a particular processor speed.

#### 7. Change to Description of Section 2.9.1, Front Panel Audio Connector/Jumper Block

Section 2.9.1, Front Panel Audio Connector/Jumper Block will change in its entirety as follows:

### 2.9.1 FRONT PANEL AUDIO CONNECTOR/JUMPER BLOCK

### **!** CAUTION

Do not place jumpers on this block in any configuration other than the one described in Table 41. Other jumper configurations are not supported and could damage the Desktop Board D865PERL.

This connector has two functions:

- With jumpers installed, the audio line out signals are routed to the back panel audio line out connector.

- With jumpers removed, the connector provides audio line out and mic in signals for front panel audio connectors.

Table 41 describes the two configurations of this connector/jumper block.

Table 41. Front Panel Audio Connector/Jumper Block

| Jumper Setting                           |                      | Configuration                                                                                                                                                                                                                                                      |

|------------------------------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 2<br>3 0 0 4<br>5 0 6<br>7 0<br>9 0 10 | 5 and 6<br>9 and 10  | Front out signals if 6-channel audio (line out signals if 2-channel audio) are routed to the back panel line out connector. The back panel audio line out connector is shown in Figure 19 on page 60.                                                              |

| 1                                        | No jumpers installed | Mic in and front out signals if 6-channel audio (line out signals if 2-channel audio) are available for connection to front panel audio connectors.  Table 28 on page 64 lists the names of the signals available on this connector when no jumpers are installed. |

### **★** INTEGRATOR'S NOTE

When the jumpers are removed and this connector is used for front panel audio, the back panel audio line out and mic in connectors are disabled.

### **DOCUMENTATION CHANGES**

The Documentation Changes listed in this section apply to the *Intel® Desktop Board D865PERL Technical Product Specification* (Order Number C31764). All Documentation Changes will be incorporated into a future version of that specification.

1. Removal of Intel® Branding From Subtitle of Section 1.10.2

Section 1.10.2 Subtitle will change as follows:

### 1.10.2 FLEX 6 AUDIO SUBSYSTEM